## CONVERTITORE DIGITALE/ANALOGICO A RESISTENZE PESATE

(Esercizio n°12.25 pag. 547, Jaeger: Microelettron ica)

Descrizione del problema

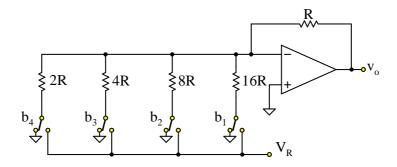

Il circuito mostrato in Fig. 1 rappresenta un convertitore digitale analogico (DAC) a 4 bit con rete resistiva del tipo a resistenze pesate. Assumendo un amplificatore operazionale ideale, determinare l'espressione della tensione di uscita in funzione della generica cifra binaria  $b_1b_2b_3b_4$ . Si determini inoltre il valore della tensione di uscita in corrispondenza della cifra binaria 0111.

Dati:

$$V_R = 3.2 \text{ V}$$

,  $R = 10 \text{ k}\Omega$

Soluzione

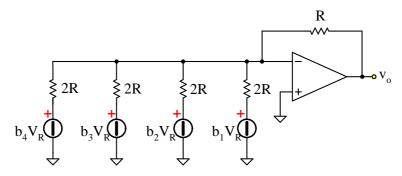

Come si evince dalla Fig. 1, i bit corrispondenti alla cifra binaria da convertire, tramite la posizione dei deviatori elettronici determinata dal valore 0 o 1 del bit corrispondente, causano l'applicazione di una tensione nulla oppure pari a V<sub>R</sub> all'ingresso corrispondente. Pertanto, tali deviatori possono essere sostituiti da generatori equivalenti, secondo quanto mostrato in Fig. 2. Il circuito che ne deriva è quello di un semplice sommatore in cui la tensione di uscita risulta data dalla seguente espressione:

(1)

$$v_o = -\frac{R}{2R}b_4V_R - \frac{R}{4R}b_3V_R - \frac{R}{8R}b_2V_R - \frac{R}{16R}b_1V_R = -2^{-4}V_R\sum_{i=1}^4 2^{i-1}b_i$$

Come si può osservare ciascun ingresso è pesato secondo il valore della corrispondente cifra binaria. Al bit meno significativo corrisponde una tensione di uscita pari a 200 mV.

La tensione di uscita in corrispondenza della cifra binaria 0111 vale -2.8 V. Nella tabella seguente riportiamo i 16 valori possibili della tensione di uscita in corrispondenza dei diversi valori della cifra binaria d'ingresso.

| $b_4$ | $b_3$ | $b_2$ | $b_1$ | v <sub>o</sub> [V] |

|-------|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 0     | 0.0                |

| 0     | 0     | 0     | 1     | 0.2                |

| 0     | 0     | 1     | 0     | 0.4                |

| 0     | 0     | 1     | 1     | 0.6                |

| 0     | 1     | 0     | 0     | 0.8                |

| 0     | 1     | 0     | 1     | 1.0                |

| 0     | 1     | 1     | 0     | 1.2                |

| 0     | 1     | 1     | 1     | 1.4                |

| 1     | 0     | 0     | 0     | 1.6                |

| 1     | 0     | 0     | 1     | 1.8                |

| 1     | 0     | 1     | 0     | 2.0                |

| 1     | 0     | 1     | 1     | 2.2                |

| 1     | 1     | 0     | 0     | 2.4                |

| 1     | 1     | 0     | 1     | 2.6                |

| 1     | 1     | 1     | 0     | 2.8                |

| 1     | 1     | 1     | 1     | 3.0                |

Fig. 1– Schema di un convertitore digitale/analogico (DAC) a 4 bit con rete a resistenze pesate

Fig. 2– Schema equivalente del convertitore digitale/analogico a 4 bit con rete a resistenze pesate